14) Работа МПС в режиме прерывания.

Прерывания делятся на внешние аппаратные и внутренние. Запросы прерываний IRQ (Interrupt Request) внешних аппаратных прерываний поступают в систему прерываний или на линию немаскированного прерывания NMI МП. Система прерывания формирует сигнал INTR маскированного прерывания МП. Маскированное прерывание отличается от немаскированного тем, что первое может быть запрещено программно — командой сброса флага разрешения прерываний IF. В этом случае при поступлении запросов прерывания они будут игнорироваться.

Внутренние прерывания процессора разделяют на программные и аппаратные. Источниками внутренних программных прерываний являются: ошибка деления; пошаговый режим; команда INTO.

Внутренние программные прерывания INT n и INT 3 выполняются по команде прерывания и разрешают вызывать подпрограммы обработки прерываний (например, сервисные подпрограммы BIOS и DOS) без применения дальних вызовов подпрограмм. В отличие от INT n, прерывание INT 3 является однобайтной командой и обычно используется для передачи управления подпрограмме-отладчику. Выполнение программных прерываний не зависит от флага разрешения прерывания IF.

Внутренние аппаратные прерывания процессора возникают в следующих случаях:

при делении на ноль (тип 0);

при установленном флаге трассировки (тип 1). В этом случае прерывание происходит после выполнения каждой команды;

после команды INTO (тип 4), если установлен флаг переполнения OF.

Аппаратные прерывания возникают при активном уровне сигналов на выводах NMI и INTR. Маскированные прерывания выполняются при установленном флаге IF. При переходе к подпрограмме обработки аппаратного прерывания процессор последовательно формирует два цикла подтверждения прерывания, в которых генерируется сигнал INTA . После второго импульса INTA контроллер прерываний передает по шине данных номер вектора прерывания n. Далее действия процессора аналогичны выполнению программного прерывания. Обработка текущего прерывания может быть прервана немаскированным прерыванием или другим маскированным прерыванием высшего приоритета в том случае, если подпрограмма-обработчик установит флаг разрешения прерывания IF. Немаскированное прерывание выполняется независимо от состояния флага IF.

Прерывание. В микропроцессоре существуют средства обработки запросов прерываний восьми уровней. Если одно из внешних устройств, соединенных с системой прерывания МП, инициирует запрос прерывания, то система формирует сигнал Н-уровня на выводе INT МП. Одновременно система прерывания посылает на шину данных код команды rst v (прерывание по вектору v). Вектор v представляет собой код, который указывает адрес начальной команды в подпрограмме обслуживания данного запроса прерывания.

Последовательность действий МП в режиме прерывания следующая:

Прием запроса прерывания и блокирование входа запроса прерывания.

Прием команды rst v.

Сохранение адреса возврата (содержимого указателя команд) в стеке.

Формирование адреса подпрограммы обслуживания запроса.

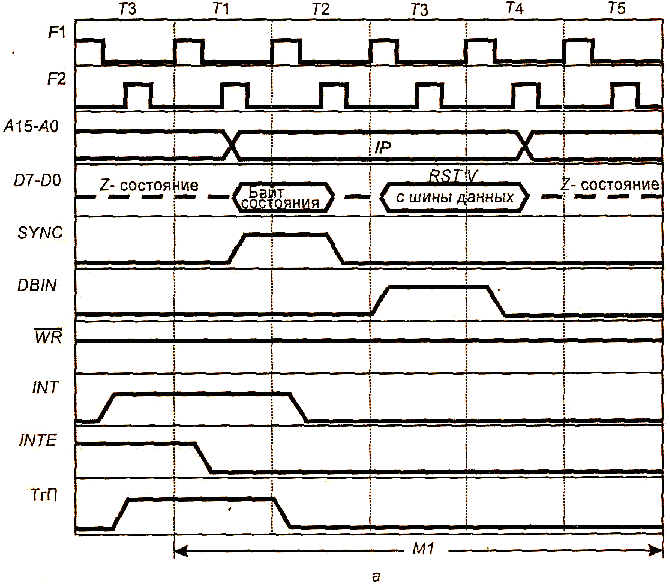

Запросы прерывания МП принимаются со входа INT МП триггером прерываний, которым управляет триггер разрешения прерываний. В свою очередь, триггер разрешения прерываний можно программным способом установить в логическую единицу или ноль. Состояние логической единицы триггера разрешения прерываний разрешает прием прерывания от входа INT, состояние нуля — запрещает. Система прерывания может установить активный уровень сигнала на линии INT в любой момент выполнения программы, однако прием его синхронизируется следующим образом. При наличии сигнала разрешения прерывания (триггер разрешения прерываний установлен в единицу) триггер прерываний устанавливается в последнем такте последнего машинного цикла команды, на протяжении выполнения которого поступил запрос. Это дает возможность процессору завершить выполнение команды, прежде чем начнется обработка прерывания. Если прерывание не разрешено (триггер разрешения прерываний сброшен в ноль), запрос прерываний по входу INT игнорируется. Временная диаграмма работы процессора показана на рис.1.11. а, б.

После приема сигнала запроса прерывания процессор переходит к выполнению цикла ПРЕРЫВАНИЕ, который состоит из трех машинных циклов. Первый из них — m1 (рис.1.11. а) — предназначен для приема команды rst v, а два других — m2 и м3 — для сохранения адреса возврата "в стеке (рис.1.11. б). В первом такте Т1 цикла m1 в байте состояния формируется сигнал подтверждения прерывания, который используется для управления чтением команды rst v.

В такте ТЗ процессор принимает по шине данных байт команды rst v, формируемой системой прерываний. В тактах Т4, Т5 цикла ПРЕРЫВАНИЯ формируется адрес первой ячейки стека, отведенной для хранения адреса возврата из подпрограммы обслуживания запроса прерывания. В циклах m2 и m3 осуществляется запись адреса возврата (содержимого указателя команд) в стек. В следующем цикле выбирается первая команда подпрограммы обслуживания прерывания по адресу, определяемому командой rst v.

Рис.1.11. Цикл ПРЕРЫВАНИЕ: а — M1.

Рис.1.11. Цикл ПРЕРЫВАНИЕ:

6 — M2 и М3; ТгП — триггер прерывания

В частном случае с помощью подпрограммы осуществляется хранение содержимого основных рабочих регистров процессора, управление триггером разрешения прерывания, восстановление содержимого регистров и возврат в основную программу (восстановление содержимого указателя команд).